# 高効率電子放出素子(HEED)の特性改善とその応用

Improvement of a High Efficiency Electro-emission Device (HEED) Characteristics and its Application

根岸伸安,酒村一到,山田高士

Nobuyasu Negishi, Kazuto Sakemura, Takashi Yamada

佐藤 英夫,吉川 高正,小笠原 清秀

Hideo Sato, Takamasa Yoshikawa, Kiyohide Ogasawara

要 旨 高効率電子放出素子(HEED)の素子構造の改良を行った。その結果,放出電子の安定性向上と,駆動電圧の大幅な低減が同時に達成された。

この改良型HEEDを電子源に用いた4インチサイズのディスプレイパネルの試作を行い、動作の確認をした。

Summary It is shown that the emission characteristics of a previously reported MIS-type electron emission device termed HEED (High Efficiency Electro-Emission Device) can be significantly improved by appropriate arrangements of the emission site structures. Using this emitter as an excitation source, a 4-inch prototype flat panel display has been fabricated on a glass substrate. The panel operates well at a practical brightness of 2000 cd/m<sup>2</sup>.

キーワード : 電子放出, HEED, フラットパネルディスプレイ, 安定性, 駆動電圧低減, 高輝度

# 1. まえがき

冷電子放出素子は,フラットパネルディスプレイへの実用に向けて,盛んに研究が行われている $^{(1),(2),(3),(4)}$ 。また,真空マイクロエレクトロニクスへの応用への研究も行われている $^{(5)}$ 。1997年,我々は従来の冷電子放出素子に比べて非常に高い電子放出効率と電子放出電流を持つ素子を見出した $^{(6)}$ 。この素子はPt/Si $^{(6)}$ 3、この素子はPt/Si $^{(6)}$ 3、層の膜厚がそれぞれ5 $^{(6)}$ 4のnmと非常に厚い点が特徴であった。また,一般的な成膜技術で容易に,そして低コストで作製で

きるという利点も持っている。我々はこの素子を高効率電子放出素子(HEED:High Efficiency Electro-emission Device) と名付け, 開発を続けてきた(7),(8),(9)。

しかしながら,開発初期のHEED は駆動電圧が高く,例えばフラットパネルディスプレイの電子源として実用化するには低電圧化などの特性改善が必要であった。また放出電子による発光の安定性に問題があった。そこで,我々はエミッションサイト形成および炭素層の付与など,素子構造の改良によって電子放出電流を下げることなく駆動電圧の大幅な低

減と発光の安定化に成功した。またフラットパネルディスプレイ用電子源としての可能性を確認するために4インチサイズのディスプレイパネルの試作を行った。

#### 2. 実験方法

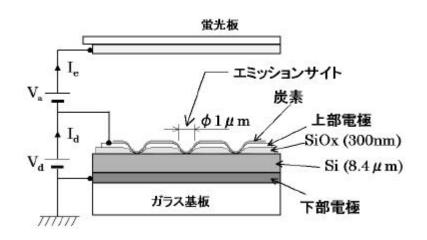

図1に本素子の断面構造と測定システムの概略を示す。洗浄したソーダライムガラス基板に下部金属電極,シリコン層,SiO $_{\rm x}$ 層,上部金属電極,炭素層の順で成膜を行い,金属/絶縁体/半導体(MIS)タイプの素子を作製した。それぞれの層は一般的な真空成膜法を用いて形成することができる。シリコン層とSiO $_{\rm x}$ 層の膜厚はそれぞれ $_{\rm x}$ 8.4  $_{\rm x}$   $_{\rm x}$   $_{\rm x}$  300nm である。

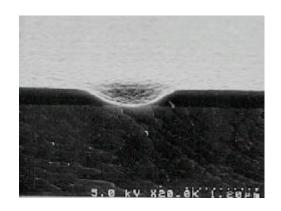

図中に示すように素子表面には直径約1μmのエミッションサイトが形成されている。このエミッションサイトはシリコン層の成膜後、SiO<sub>x</sub>層および上部金属電極を成膜する際にマスクを用いて形成することができる。本実験の場合、素子表面でのエミッションサイト密度は1mm²あたり1000サイトである。このサイト密度を変えることによって電子放出密度をコントロールすることも可能である。サイトの断面は直径約1μmのくぼんだ形状をしており、SiO<sub>x</sub>層と上部金属電極のそれぞれの膜厚がサイトの中心に向かって徐々に減少していくという大変ユニークな形状をしている。サイト形成後、炭素層はサイトを含めた素子表面の全体を覆うよ

うに成膜を行った。図2はエミッションサイト 断面のSEM(Scanning Electron Microscope)写 真である。

図2 エミッションサイト断面の SEM 像

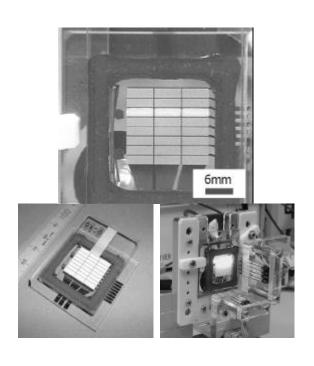

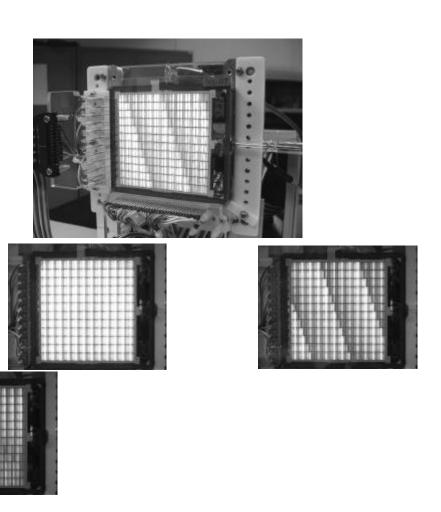

次に本実験に用いた実験パネルの外観を示す (図3)。まず、44mm×44mm、厚さ2.8mmのソーダライムガラス基板上にマトリクス状にこの素子を作製し、素子側基板とした。画素はメタルマスクを用いてパターンニングを行っている。1つの画素サイズは2mm×6mmで3×8画素のマトリクスになっている。蛍光板にはソーダライムガラス基板上にITO膜を電極膜として成膜した後、P-22蛍光体を塗布したものを用いた。

素子基板と蛍光板との間隔が3mmとなるようにガラス製のスペーサーを用いて張り合わせ, 真空に封止して実験パネルとした。封止には一般的なフリットガラスを用いた。封止時の温度

図1 素子断面構造と測定システムの概略

は約450 である。

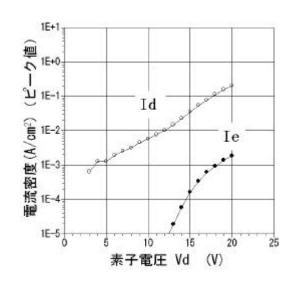

電流 - 電圧特性の測定は図1に示すように, 素子印加電圧 Vdによって素子に流れるダイオード電流を Id, エミッションサイトから放出されるエミッション電流 Ie とし測定を行った。素子 - 蛍光面間に印加した加速電圧 Va は1k V(一定)である。また,電子放出のメカニズムを調べるために,F-Nプロットによる解析と放出電子のエネルギー分布の測定を行った。

図3 実験パネル外観

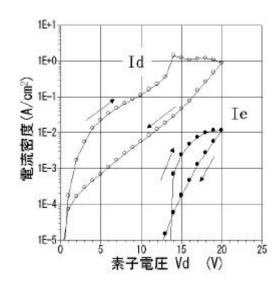

図 4 電流 - 電圧特性(DC)

### 3. 結果と考察

図4にDC駆動での電流・電圧特性のグラフを示す。素子電圧 Vdを直流電圧で20Vまで0.3V/sec.の速度で電圧掃引した。グラフのように0Vから20Vまで正方向に電圧を掃引したとき14V付近に電流のピークがあらわれ,同時にエミッション電流が観測されるようになる。その後,さらに電圧を上げるとエミッション電流はさらに増大し,20Vにおいて10mA/cm²に達する。以前報告したHEED は Vd = 110Vにおいてエミッション電流密度は1.4mA/cm²であった(6)。これに比べて本実験において大幅に駆動電圧が低減していることがわかる。これらのDC駆動でのプロセスはエミッション電流を得るために必要なプロセスである。

図4の電流・電圧特性で観測される負性抵抗は恐らくSiOx層でトラップされた電子によるものと推測される。SiOx層に注入された電子は多くのトラップ準位によって捕獲され、固定された電荷として働くと考えられる。グラフよりVd = 14VではSiOx層での厚さ方向に沿った電位分布が曲げられていると思われる。つまり、下部電極近傍のSiOx層では電界が弱められ、一方、表面電極側近傍では電界が強化される。この表面側の高い電界強度により電子が放出されるようになる。

図 5 電流 - 電圧特性(パルス)

DC駆動の後,パルス駆動で電流-電圧特性の測定を行った(図5)。駆動周波数は60 H z ,パルスデューティーは1/120 である。Vd = 20Vにおいて1.8mA/cm²(ピーク値)のエミッション電流密度が観測されている。またこのときの電子放出効率は約1%であった。蛍光面での発光パターンを観察したが,以前のHEED に比べて時間的な揺らぎが大幅に改善していることを確認できた。

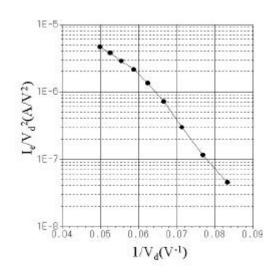

図6にパルス駆動でのF-N プロットを示す。 約15V以下での領域でF-N プロットの直線性が みられている。これはこの電圧領域においての 電子放出は電界効果によるものであることを示

図6 F-N プロット

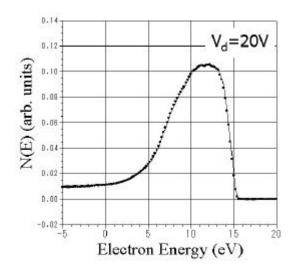

図7 放出電子のエネルギー分布

している。高電界領域で直線からはずれている のは、何らかの原因で電流注入が押さえられて いるためと考えられ、今後の検討課題である。

図7はDC駆動(Vd=20V)での放出電子のエネルギー分布である。グラフより放出電子は非常に高いエネルギーを持っていることがわかる。この結果からエミッションサイトより放出される電子は準弾道的なホットエレクトロンであると考えられる。

このF-Nプロットと放出電子のエネルギー分布の結果は,先に記した,SiO<sub>x</sub>層の表面側に強電界が生じ,そこで加速された電子が放出するというモデルを支持している。

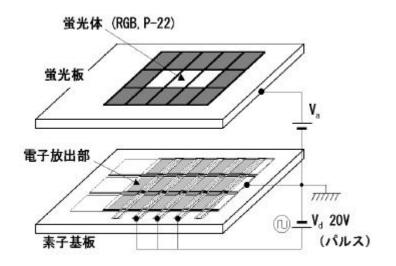

#### 4.4インチ試作パネル

フラットパネルディスプレイの電子源への応用可能性を調べるために対角4インチのパネルディスプレイの試作を行った。図8に試作パネルの構造の模式図を示す。

表示エリア大きさは 72mm × 72mm, 画素数は 12 x RGB x 12 でサブピクセルサイズは 2mm x 6mm である。先の実験パネルと同様に基板に 2.8mm 厚のソーダライムガラスを基板に使用 し、メタルマスクによるパターンニングでマト リックス状画素の形成を行った。まず,ガラス 基板上に12本の下部電極を形成した。その後シ リコン層を成膜し,次にSiO、層と上部電極膜 を成膜する際にエミッションサイトを形成し た。最後に炭素層と36本のバス電極を形成し た。蛍光板にはソーダライムガラス基板にRGB の蛍光体とブラックマトリクスをコーティング し、その後メタルバック層を形成したものを用 いた。蛍光面と素子表面の間隔が9mmになるよ うスペーサーを挟み ,フリットガラスを用いて 真空封止を行った。なお本試作では収束電極や リブは特に設けなかった。駆動は図8に示すよ うに素子電圧 Vd=20V でパッシブマトリクス駆 動を行った。駆動周波数は実験パネルと同様に 60Hz,パルスデューティーは1/120である。加 速電圧 Va は 7kv まで印加した。

図9に試作パネルの駆動時の様子を示す。放 出電子の広がり角が小さいので収束電極やリブ が無くても問題無く表示ができていることがわ かる。また面内の均一性も良い。加速電圧Va=7kv のとき 2000 $cd/m^2$  の輝度を得ることができた。表 1 に試作パネルの主なスペックを示す。

図8 試作パネルの構造模式

図9 駆動中の試作パネル

表 1 試作パネルスペック表

| Driving voltage                | 20 V                            |

|--------------------------------|---------------------------------|

| Pulse width                    | 139 μ sec.(60Hz)                |

| Accelerating voltage           | ~10 kV                          |

| Brightness                     | 2000 cd/m <sup>2</sup> (Va=7kV) |

| Active area                    | 4 inches                        |

| Color/Monochrome               | Color                           |

| Rows/Columns                   | 12/12                           |

| Pixel size                     | 6.0 mm x 6.0 mm                 |

| Distance (device-anode plates) | 9 mm                            |

| Gray scale                     | 15 steps                        |

| Substrate                      | Soda-lime glass                 |

#### 5. まとめ

我々はHEEDのエミッション特性を改善することに成功した。エミッションサイトの形成および素子表面への炭素層の付与など、素子構造の改良によってエミッション電流密度を低減することなく20Vまでの低電圧化を実現した。

また,パルス駆動において1.8mA/cm²(ピーク値)という大きなエミッション電流密度が得られた。エミッションパターンの時間的揺らぎも以前のHEEDと比べて大幅に低減されている。

またエミッションサイトからの放出電子は ビーム広がり角度が小さく、非常に高いエネル ギーを持つという特徴を持っている。

さらにフラットパネルディスプレイの電子源としての実用性を確認すべく 4 インチパネルディスプレイの試作を行った。画素数は 12 × RGB × 12 において駆動電圧20Vのパッシブマトリクス駆動を行ったところ,安定性,面内均一性の良い表示パターンと加速電圧7kvにおいて2000cd/m²の輝度を得ることができた。

これらの結果から,この改良型 HEED はフラットパネルディスプレイの電子源として将来有望であると考える。また,改良型 HEED の特徴を生かした電子源としての他の応用にも今後非常に期待している。

#### 6.謝辞

本研究を行うにあたり,多大なる御助言を頂きました東京農工大学 越田義信教授に深く感謝いたします。

#### 参考文献

- (1)T.Yamada etal.:IDW'02,pp.1037-1040(2002)

- (2)S.Uemura etal.: IDW'02,pp.1025-1028(2002)

- (3)N.Koshida etal.:IDW'02,pp.1029-1032(2002)

- (4)T.Kusunoki etal.:IDW'02, pp.1041-1044 (2002).

- (5)瀧口,他:信学技報,EID2002-58,pp21-24 (2002)

- (6) N. Negishi etal.: Jpn. J. Appl. Phys. 36, L939-L941 (1997).

- (7)吉川,他:1997年秋季 応用物理学関係連合講演会,No.0,pp.29(1997).

- (8)中馬,他:PIONEER R&D,8,No.3,pp.14-21 (1998).

- (9) 山田, 他: 2000 年春季 応用物理学関係連合講演会 No.2, pp.759(2000).

#### 筆 者

根岸 伸安(ねぎし のぶやす)

- a. 研究開発本部,総合研究所,高機デバイ ス研究部

- b.1990年4月

- c. 光磁気ディスクの開発を経て,現在は電子放出素子の研究開発。

## 酒村 一到(さけむらかずと)

- a. 研究開発本部,総合研究所,高機デバイ ス研究部

- b.1994年4月

- c. ポリマー二次電池の開発を経て,現在は電子放出素子の研究開発

- 山田 高士(やまだ たかし)

- a. 研究開発本部, PDP 開発センター

- b.1990 年 4 月

- c.CD-R の記録材料の開発,電子放出素子の研究開発を経て,現在はPDPの開発。

#### 佐藤 英夫(さとう ひでお)

- a. 研究開発本部,総合研究所,表示デバイ ス研究部

- b.1981年2月

- c. ロボット,画像認識などの自動化機器の 開発を経て,現在は有機半導体及び電子放 出素子の研究開発。

- 吉川 高正(よしかわ たかまさ)

- a. 研究開発本部,総合研究所,高機デバイ ス研究部

- b.1978年4月

- c. 光磁気ディスクの開発を経て,現在は電子放出素子の研究開発。

- 小笠原 清秀(おがさわらきよひで)

- a. 研究開発本部,総合研究所

- b.1972 年 4 月

- c. ハイポリマー振動膜の研究開発, リボンセンダストヘッドの研究開発, 光磁気ディスクの開発研究を経て, 現在は電子放出素子の研究開発。